# FROM POWER PACKAGES TO 3D INTEGRATION : THE THERMAL CHALLENGE

**Journée Thématique :**

Caractérisations Thermo-physiques et applications micro-électroniques

**Christophe SERRE**

## Innovation Drivers and Consequences

+Functionnality: camera,radio,TV,GPS ,games,internet.==>*integration* +Mobility: reduced form factor,weight... ==>*miniaturization*

+Performance: pixels,speed,reliability ,less energy greedy..==> *techno. breakthroughs*

-Price: more for less ==>cost reduction

Weigth 3X less Volume 5X less

## **3D PACKAGING ROADMAPS**

dation deser.

2009

Time

#### AMKOR Technology Depth 41 ( Device Roadmap: Baseband/ DSP/ App. ASIC POP - Available PKG 64 - KGD 121 ----35 55 $\checkmark$ Chip-in Substrate PS-VIBGA+S-CSP PSfcCSP Package Trend Memory Integration -8 **WLPoP** Integration 0.50 -TSV on WLCSP mr. Embedded Si + - Full array CSP Memory Flip-Stack CSP SCSP ..... ..... 3+1 SCSP TSV-SIP PS-fcCSP with Interposer - Ultra thin bottom PKG - Full array CSP - KGD - Thin bottom PKG - KGD Cell Phone SiP FC-CSP FBGA MLF® (QFN) TAPP 2006 2008 300 🇱 ASE TECH FORUM 2007 @ ASE Group. All rights reserved. 0.13µm CMOS Node Dynamics Device 300m5W Average Dis Size 49mm 62005 Arekor Technology, Inc.

## ASE

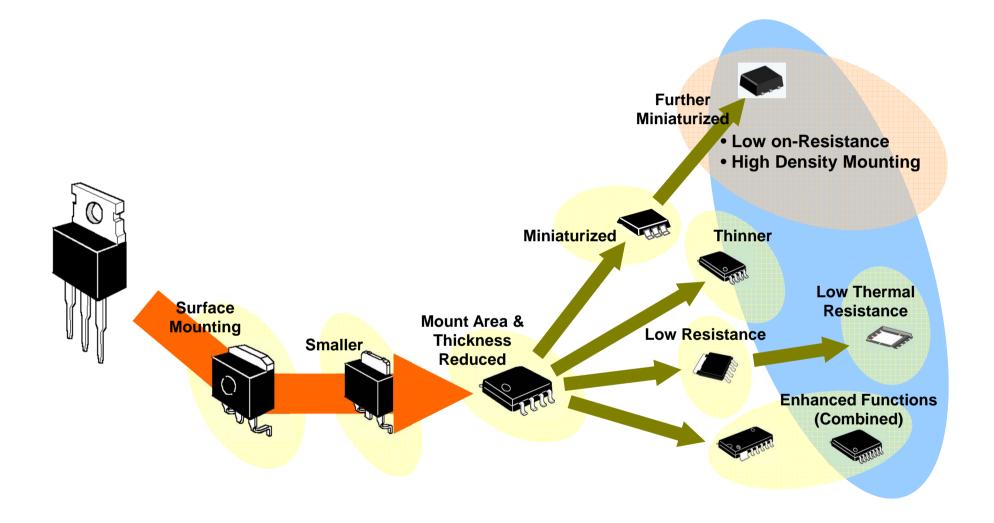

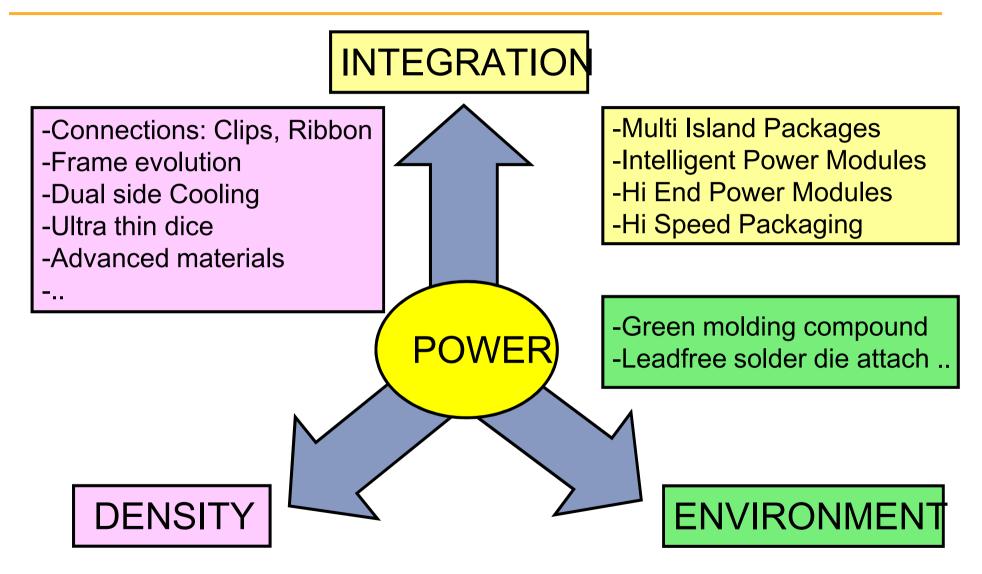

## **POWER PACKAGING CHANGES**

## **HEAT EFFECT : THE CHALLENGE!**

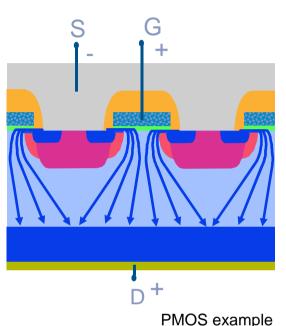

- Electric Power  $\rightarrow$  Pe = Ron \* I^2

- Dissipated Power  $\rightarrow$  Pd= (Tj Tc) / Rthj

- $Pd = Pe \rightarrow Minimum Ron, Minimum Rth$

**Key Factors for Power Packaging Efficiency**

- Interconnections

- Die Attach

- Materials

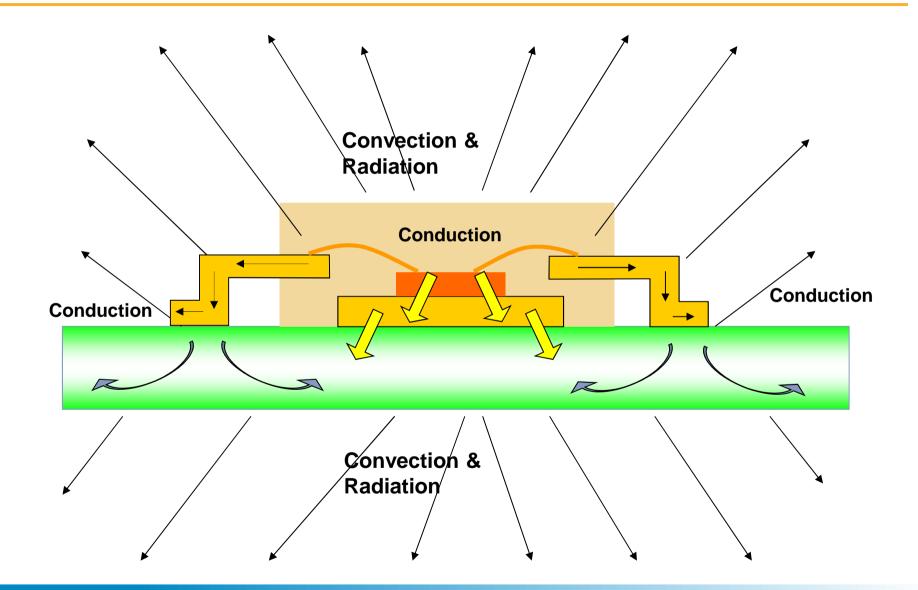

## >NATURAL WAYS

**Conduction :** heat transfer mechanism due to thermal excitation at molecular level, by direct contact. No motion of material is associated to this mechanism

Radiation : transport of electromagnetic energy

>Natural convection : transfer of heat associated with the movement of material in a fluid (liquid or gas).

## **FORCED WAYS**

>Forced convection

Components able to absorb heat with power (Pelletier effect, refrigerating machines)

>Use of some materials 's latent heat of phase change (caloducs, thermo-siphons, fluids evaporation, etc...)

## **HEAT DISSIPATION MODES**

| ≻S |                                                                                                                                                                                                                                                                                                                | ie 140W/mK@25°C, 113W/mK@100°C &<br>88W/mK@150°C                                                                                                                                                                           |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _  | i <b>lass =</b> 1.2 W/m.k<br><b>apphire</b> = 42 W/m.k                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                            |

|    | <ul> <li><b>copper</b> = 260 to 400 W/m.K</li> <li>Alloy 194 = 260</li> <li>KFC, FPG = 360</li> <li>Cub2 = 370</li> <li>Cua1= 390</li> <li>Alloy42 (FeNi) = 40</li> <li><b>/A materials</b></li> <li>PbSnAg = 30 to 45</li> <li>PbSn5Ag1.5 = 42, PbSn5Ag2.5=44, SnPb3</li> <li>Silver glue = 2 to 6</li> </ul> | <ul> <li>Resins</li> <li>Standard EMC (fused silica) = 1</li> <li>Conductive EMC (crystallized silica) = 2.5</li> <li>Ceramics</li> <li>Al2O3 = 20 to 25</li> <li>AIN =170-180</li> <li>Wires</li> <li>AI = 200</li> </ul> |

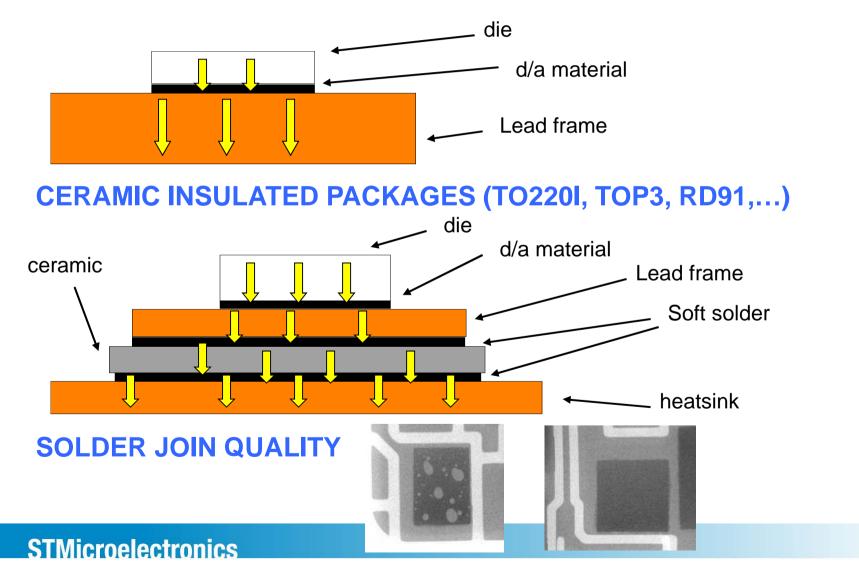

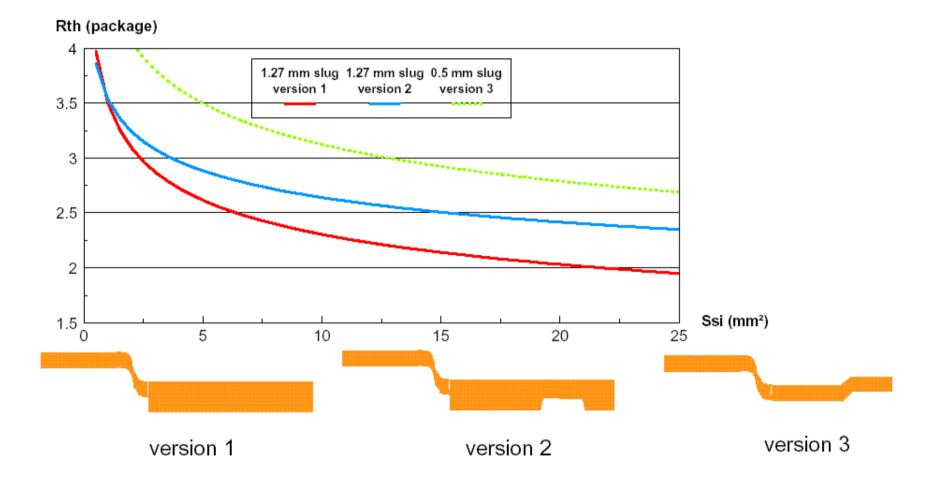

## **MULTIPLE INTERFACES EFFECT ON Rth**

### NON INSULATED PACKAGES (TO220, TO247, DPAK,...)

## **DIE THICKNESS REDUCTION**

- To improve the thermal performance of our devices by reducing the silicon thickness

- Special F/E-B/E manufacturing process to solve the warpage and the handling problem that occurs when we reduce the wafer thickness down to 100µm or below

with die thickness of 300  $\mu$ m, periphery of 200  $\mu$ m &  $\sigma$ (Si) of 110 W/mK

#### □Non insulated Insertion packages (TO220, TO247,...)

Inserted in through hole technology boards

Secured to external heatsink using screws or clip (cheaper)

#### □Insulated insertion packages (ISOWATT220, ISO218, ..)

When insulation is mandatory, thin sheet of mica or adhesive mylar can be placed between slug and heatsink

Problem : thermal performance inconsistent (variations in thickness, position and adhesion of the insulating sheet)

| PACKAGE                   | ISOLATION  | Rthj-c °C/W |

|---------------------------|------------|-------------|

| TO-220                    | none       | 1.3         |

| TO-220                    | 100mm mica | 3.3         |

| TO-220                    | mylar      | 4.4         |

| IS <mark>OWATT2</mark> 20 | none       | 3.0         |

| IS <mark>OWATT2</mark> 21 | none       | 3.8         |

| IS <mark>OWATT2</mark> 18 | none       | 2.1         |

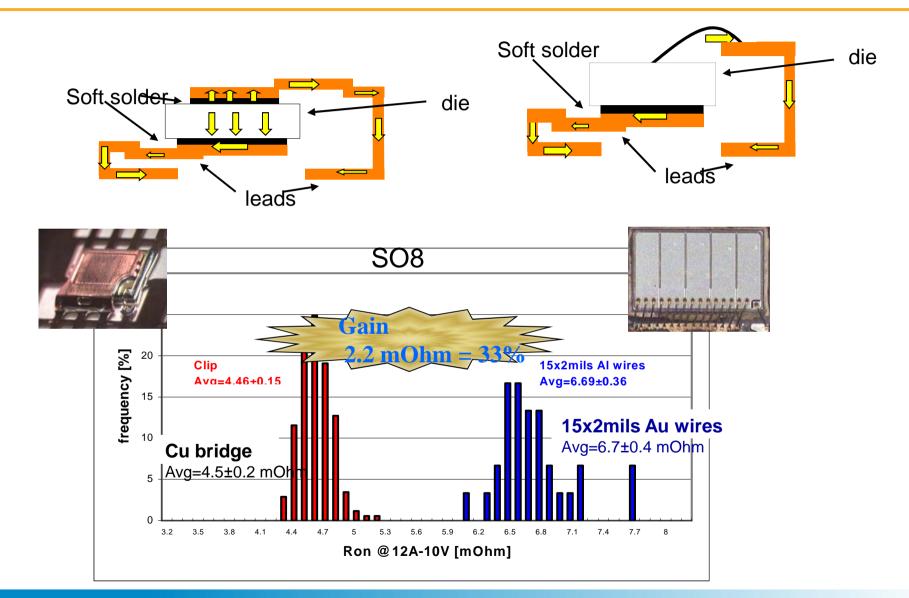

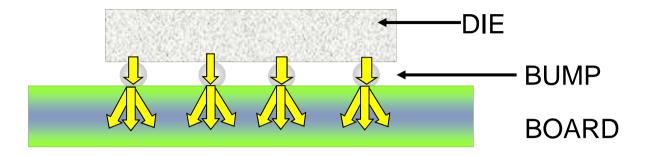

## **DIE TOP INTERCONNECTION EFFECT ON Rth**

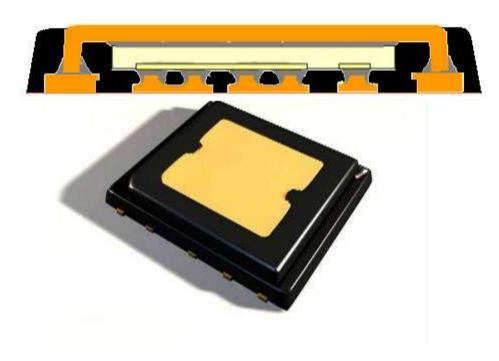

## **DUAL SIDE COOLING**

Rth improvement: Dissipation by Top

| Tour             |

|------------------|

| S,               |

| 201              |

| 0                |

| Nov              |

| 18 <sup>th</sup> |

|                  |

## WAFER LEVEL SIMILARITIES

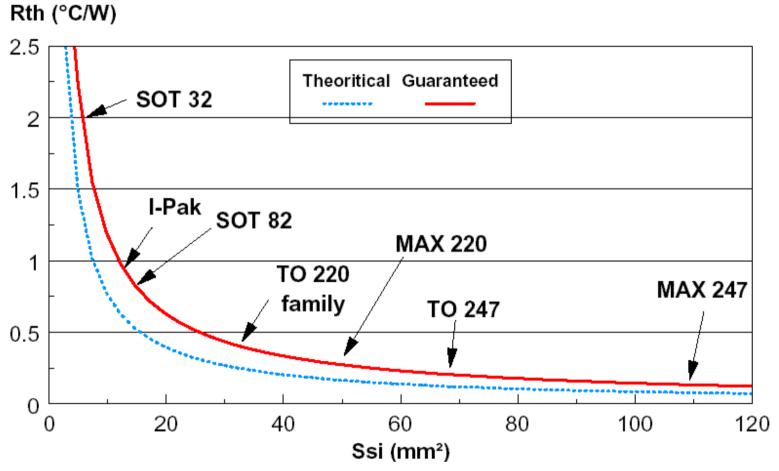

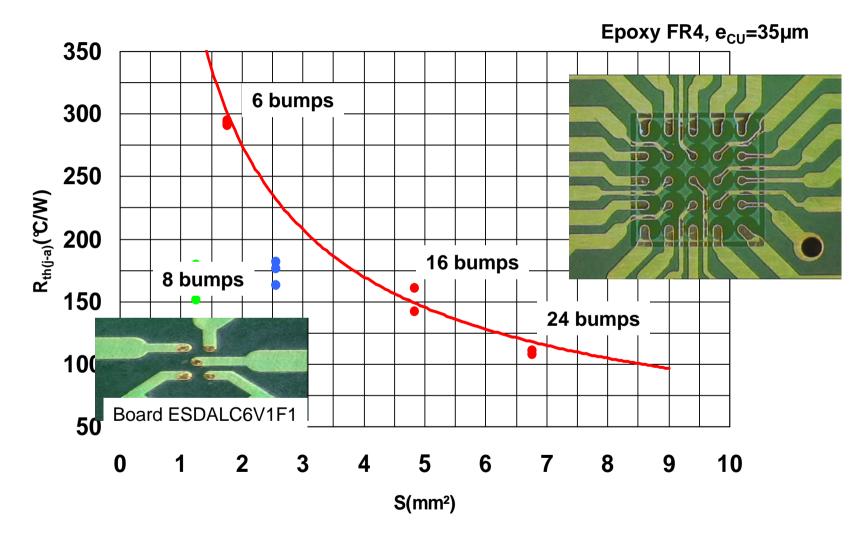

## **DIE SIZE / IO NUMBER EFFECT ON Rth**

Thermal resistance junction to ambient versus die surface (typical values) STMicroelectronics

|                                                   | D-Pak<br>Rth (j-a) | D²-Pak<br>Rth (j-a) |

|---------------------------------------------------|--------------------|---------------------|

| On infinite heatsink                              | 2.5 °C/W           | 1 °C/W              |

| FR4                                               | 65 °C/W            | 50 °C/W             |

| FR4 with 10 cm <sup>2</sup> on board heatspreader | 40 °C/W            | 35 °C/W             |

| FR4 with copper filled holes on heatsink          | 13.5 °C/W          | 12 °C/W             |

| IMS floating in air                               | 9.5 °C/W           | 8 °C/W              |

| IMS with external heatsink                        | 4.5 °C/W           | 3 °C/W              |

assuming a heatsink of 2 °C/W

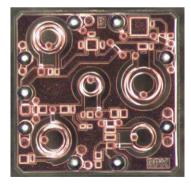

## CASE STUDY : DESIGN PARAMETERS EFFECT ON Rth

Package bottom view

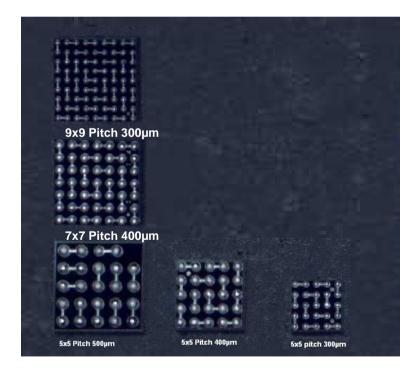

#### WCSP 3.1x2.7x0.65 mm

30 balls / Lead free (5x6 matrix) 0.3 mm diameter 0.5 mm pitch

die size =  $3.102 \times 2.738 \text{ mm}$ die thickness =  $400 \mu \text{m}$

|         | Source                                                    | Area<br>(mm²) | Power<br>(mW) |

|---------|-----------------------------------------------------------|---------------|---------------|

| Power   | Power                                                     | 2.85          | 760           |

|         | Drivers                                                   | 1.02          | 665           |

| Drivers | Digital                                                   | 3.09          | 165           |

| Digital | Total Area = 6.97 mm <sup>2</sup><br>Total Power = 1.59 W |               |               |

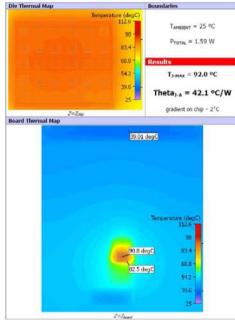

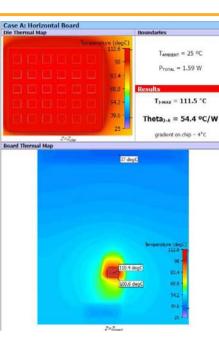

## THE CONDUCTION EFFECT IS KEY

#### Steady State Conditions

Different cases have been evaluated:

- CASE A: Horizontal board

- CASE B: Vertical board

- CASE C: Bar instead of balls

- CASE D: Die thickness 200 µm instead 400 µm

- CASE E: Layer thickness 2 oz. instead 1 oz.

- CASE F: Underfill (k = 0.4 W/mK)

| Case                         | Difference to<br>Case A |

|------------------------------|-------------------------|

| Case A<br>(Horizontal Board) |                         |

| Case B<br>(Vertical Board)   | -2.9 %                  |

| Case C<br>(Bar)              | +0.5 %                  |

| Case D<br>(Die Tck 200 µm)   | +1.3 %                  |

| Case E<br>(Layer Tck 2 oz.)  | -22.5 %                 |

| Case F<br>(Underfill)        | -0.4 %                  |

## **OTHER THERMAL EFFECTS**

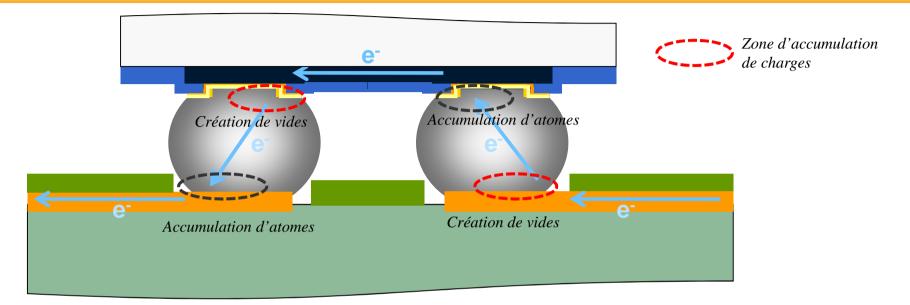

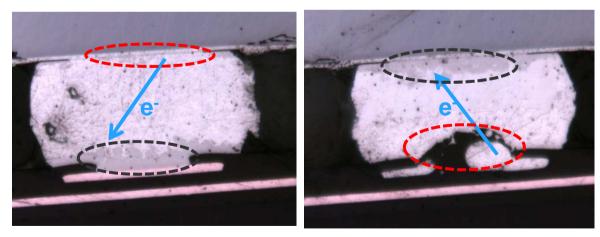

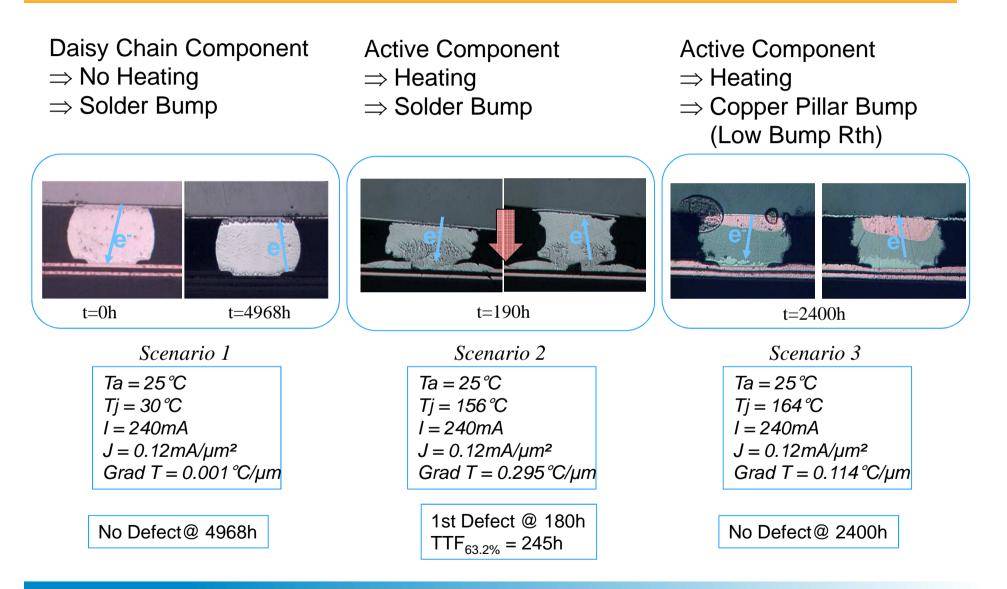

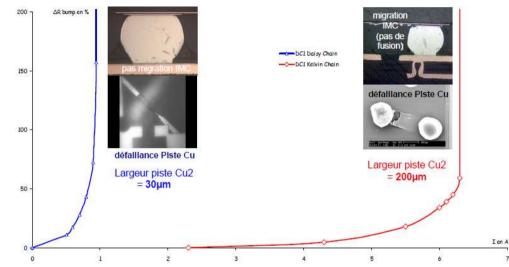

Electro migration

Black's law

$$TTF = A \cdot J^{-N} \cdot \exp\left(\frac{E_a}{k \cdot T}\right)$$

**Ukey** factors :

**Current Density J**

**Temperature T**

□Main failure mode :

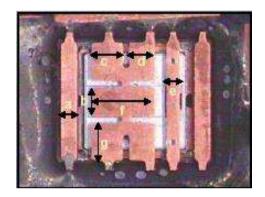

**Current crowding in some particular location heats the structure.**

❑Voids are created, increasing the current density and the heating of the structure

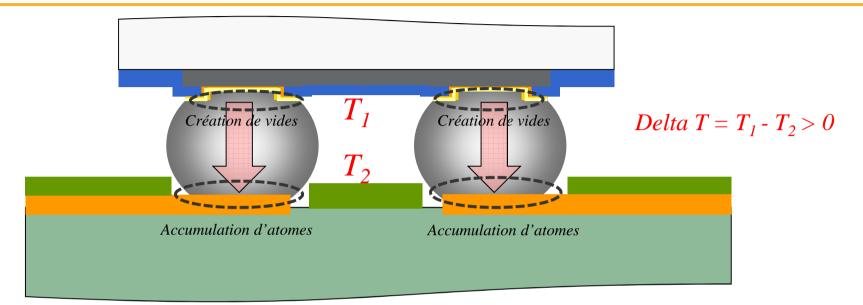

#### □Thermo migration

The component ambient operating temperature can drastically influence the aging speed. Especially a temperature gradient between the component and the board (from 0.15°C/µm) can damage the bump

## **ELECTROMIGRATION EFFECT**

Courant électrique = 400mA T ambiante =125 °C Microsection @ 320 hours Bossage en SnAg4Cu0.5

## **THERMOMIGRATION EFFECT**

Pas de Courant électrique Delta T = 0.2 °C/µm Microsection @ 60 hours Bossage en SnAg4Cu0.5

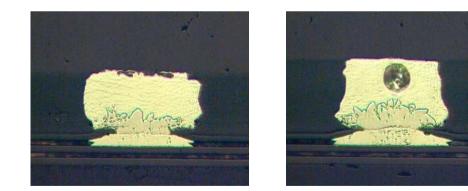

## **COMPONENT DESIGN EFFECT**

From 1 Amp to >6 Amps for the same bump => pad & trace influence

Resulting from the Joule effect, either the bump or the component structure can be heated and in certain the extend fuse.

□Key parameters are :

□The bump material

**The bump size**

The component and PWB design (Line width, Line thickness, Thermal vias,...)

The component and the PWB materials (Glass, Silicon, ...)

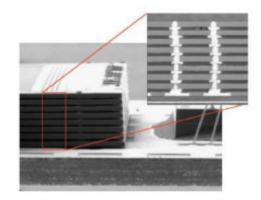

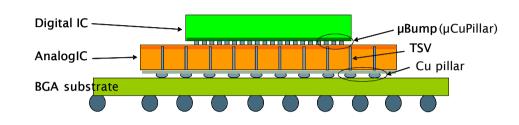

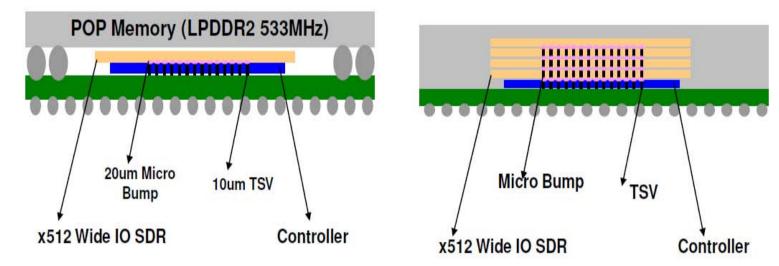

# **3D COMPONENT = 3X COMPLEXITY**

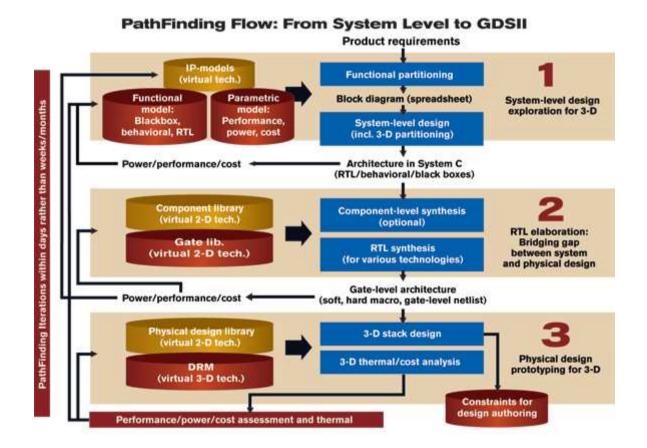

## **3D DESIGN CHALLENGES: THINK GLOBAL**

Main shift in Design paradigm: 3D means to think B-E and F-E at the same time

# **THANK YOU!**